Monday, May 29, 2023

Modul 2: Percobaan 2 Kondisi 24

Modul 2: Percobaan 1 Kondisi 25

Modul 2: Percobaan 1 Kondisi 25

Soal 8.1

• Untuk S = 0, ekspresi Boolean untuk output menjadi Y = I0.

• Untuk S = 1, ekspresi Boolean untuk keluaran menjadi Y = I1.

Jadi, input I0 dan I1 masing-masing dialihkan ke output untuk S = 0 dan S = 1. Memperluas konsep lebih lanjut, Gambar 8.5 menunjukkan diagram logika dari multiplexer 4-ke-1. Kombinasi masukan 00, 01, 10 dan 11 pada jalur pilih masing-masing beralih I0, I1, I2 dan I3 ke output. Pengoperasian sirkuit diatur oleh fungsi Boolean (8.1). Demikian pula, multiplexer 8-ke-1 dapat direpresentasikan dengan fungsi Boolean (8.2):

8.1.2. Implementasi fungsi Boolean dengan Multiplexer

Salah satu aplikasi multiplexer yang paling umum adalah penggunaannya untuk implementasi kombinasional logika fungsi Boolean. Teknik paling sederhana untuk melakukannya adalah dengan menggunakan MUX 2n-ke-1 untuk diterapkan fungsi Boolean n-variabel. Jalur input yang sesuai dengan masing-masing minterm yang ada di Fungsi Boolean dibuat sama dengan status logika '1'. Minterm tersisa yang tidak ada di file Fungsi Boolean dinonaktifkan dengan membuat baris masukan yang sesuai sama dengan logika '0'. Sebagai seorang Contoh, Gambar 8.8 (a) menunjukkan penggunaan MUX 8-ke-1 untuk mengimplementasikan fungsi Boolean yang diberikan dengan persamaan:

2. Buka schematic capture, pilih bagian component mode (

), dan pada bagian devices klik 'P'.

), dan pada bagian devices klik 'P'.3. Pastikan kategorinya berada pada all categories agar mudah dalam melakukan pencarian.

4 .Ketikkan semua nama bahan komponen yang dibutuhkan dalam rangkaian.

5. Double klik komponen yang kita butuhkan agar komponen tersebut muncul dikolom Devices.

6. Buka bagian Terminals mode (

)

)7. Pilih terminal yang diperlukan.

8. Setelah semua komponen didapatkan, letakkan komponen pada papan rangkaian.

9. Rangkailah semua komponen sesuai prinsipnya.

10. Klik play (

) pada bagian kiri bawah aplikasi untuk menjalankan rangkaian simulasi.

) pada bagian kiri bawah aplikasi untuk menjalankan rangkaian simulasi.Input logicstate yang terhubung ke 8 pin merupakan sinyal atau inputan yang tetap dan kemudian pada pin data selector, pin ABC dapat diganti sesuai dengan inputan yang mana yang akan dilewatkan. Berdasarkan data selector maka pada output akan diteruskan inputan yang telah disesuaikan dengan data selector.

Untuk prinsip kerja rangkaian ini kita harus mengetahui tabel kebenaran dari IC 74151. Dimana X0-X7 adalah 8 pilihan input, bebas diisi dengan input digital. Y adalah output dan Y' adalah NOT dari Y. A B C adalah input selector. Input bisa kita pilih dengan mengatur kombinasi A B C. E' input yang mengatur kondisi output, jika kita berikan logika 1 maka Y akan berlogika 0.

- Biarkan Fungsi Bolean menjadi fungsi f(A,B,C)

- f(A,B,C) = ∑ 0,3,4,6,7

Modul 2 Flip-Flop

- Merangkai dan menguji rangkaian flip-flop

Flip-Flop

Flip-flop

adalah rangkaian elektronika yang memilki dua kondisi stabil dan dapat

digunakan untuk menyimpan informasi. Flip-flop merupakan pengaplikasian

gerbang logika yang bersifat Multivibrator Bistabil. Dikatakan

Multibrator Bistabil karena kedua tingkat tegangan keluaran pada

Multivibrator tersebut adalah stabil dan hanya akan mengubah situasi

tingkat tegangan keluarannya saat dipicu (trigger). Flip-flop mempunyai

dua Output (Keluaran) yang salah satu outputnya merupakan komplemen

Output yang lain.

a. R-S Flip-FlopR-S Flip-flop merupakan dasar dari semua flip-flop yang memiliki 2 gerbang inputan atau masukan yaitu R dan S. Gambar 2.3 R-S Flip-Flop

b. J-K Flip-FlopKelebihan

J-K Flip-flop adalah tidak adanya kondisi terlarang atau yanng berarti

diberi berapapun inputan asalkan terdapat clock maka akan terjadi

perubahan pada keluaran atau outputnya.c. D Flip-FlopD

Flip-flop merupakan salah satu jenis flip-flop yang dibangun dengan

menggunakan flip-flop R-S. Perbedaan dengan R-S flip-flop terletak pada

inputan R, dan D Flip-flop inputan R terlebih dahulu diberi gerbang NOT.d. T Flip-FlopT

Flip-flop merupakan rangkaian flip-flop yang telah di buat dengan

menggunakan J-K Flip-flop yang kedua inputannya dihubungkan menjadi satu

maka akan diperoleh flip-flop yang memiliki watak membalik output

sebelumnya jika inputannya tinggi dan outputnya akan tetap jika

inputannya rendah.

Gambar 2.6 T Flip-Flop

Friday, May 26, 2023

Laporan Akhir 1 Modul 1

- 1. JumperGambar 1. Jumper

1. Gerbang AND

Gerbang AND ini memerlukan dua atau lebih input untuk menghasilkan satu output. Jika semua atau salah satu inputnya merupakan bilangan biner 0, maka outputnya akan menjadi 0. Sedangkan jika semua input adalah bilangan biner 1, maka outputnya akan menjadi 1

2. Gerbang ORGerbang OR ini akan menghasilkan output 1 jika semua atau salah satu input merupakan bilangan biner 1. Sedangkan output akan menghasilkan 0 jika semua inputnya adalah bilangan biner 0.

3. Gerbang XORGerbang logika yang outputnya akan bernilai benar atau “1” jika nilai input-inputnya berbeda dan bernilai salah atau “0” jika nilainya sama. Komponen elektronika yang menggunakan gerbang logika XOR adalah IC 7486.

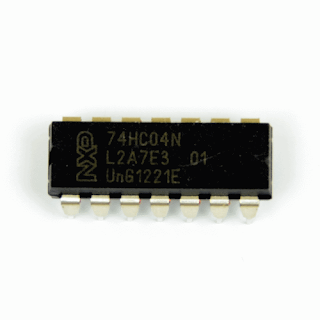

4. Gerbang NOTGerbang NOT sering juga disebut sebagai rangkaian inventer (pembalik). Tugas rangkaian NOT (pembalik) ialah memberikan suatu keluaran yang tidak sama dengan masukan. Simbol logika untuk pembalik (inverter, rangkaian NOT).

5. Gerbang XNORGerbang logika NOR-eksklusif merupakan gerbang XOR yang dibalik (inverted). Gerbang NOR-eksklusif sering kali disingkat sebagai X-NOR. Simbol standard gerbang logika X-NOR adalah seperti tampak pada gambar di samping.

6. Gerbang NANDGerbang NAND terdiri dari dua atau lebih dari masukan dan sebuah sinyal keluaran. Semua masukan harus berharga tinggi untuk menghasilkan keluaran rendah.Gambar di bawah menunjukkan struktur logika dari gerbang AND dan sebuah gerbang NOT. Keluaran akhir adalah hasil operasi NOT-AND dari masukannya. Gerbang ini lebih dikenal dengan gerbang NAND.

Percobaan ini menggunakan modul D'Lorenzo pada bagian DL2203D dan DL2203C. Pada bagian DL2203D, kita memasukkan logika dari B0 dan B1 yang kemudian dihubungkan ke gerbang logika menggunakan jumper. Logika B0 dan B1 disini kita set sesuai dengan perintah pada modul percobaan,

- Gerbang NOT

- Gerbang AND

- Gerbang OR

- Gerbang XOR

- Gerbang NAND

- Gerbang NOR

- Gerbang XNOR

- Simulasi Percobaan 1

- Simulasi Sinyal Clock

Percobaan 1

1.Analisa perbedaan sinyal hasil keluaran masing-masing gerbang logika? Jelaskan mengapa didapatkan sinyal seperti itu dan bandingkan dengan sinyal clocknya!

➤ a) Pada Gerbang Not

Output yang didapatkan sama

dengan input yang dihubungkan dengan input clock(CLK) seharusnya sinyal keluaran

/output dari Not adalah kebalikan dari sinyal masukan/ input dari lock.

b) Pada Gerbang AND

Output yang didapatkan sama

dengan input Clock yang diberikan karena dalam AND prinsip kerjanya menggunakan

perkalian dalam input sinyal CLK bernilai 0 maka outputnya juga bernilai 0

untuk input CLK yang bernilai 1 maka outputnya juga bernilai 1 karena prinsip

kerja AND adalah perkalian diinputnya.

c) Pada Gerbang OR

Output yang didapatkan sama

dengan input clock yang diberikan karena dalam OR prinsip kerjanya menggunakan

penjumlahan dalam inputnya sinyal clk bernilai 0 maka outputnya juga bernilai 0

begitu pula output 1 ia memiliki input 1 karena aturan OR yaitu Penjumlahan.

d) Pada Gerbang

XOR

Output pada sinyal XOR sama

dengan input OR yang bernilai 0 sedangkan untuk input input yang bernilai 1

berkebalikan dengan sinyal input yang diberikan prinsip kerja untuk gerbang

logika XOR adalah menghasilkan keluaran yang bernilai 1 hanya jika jumlah masukan

yang bernilai 1 adalah ganjil dan bernilai 0 jika jumlah masukan yang bernilai

1 dan genap

e) Pada Gerbang

NAND

Output pada gerbang NAND

kebalikan dari sinyal input yang diberikan, prinsip kerja NAND adalah perkalian

yang di NOT kan Dimana jika sinyal input 0 maka output perkalian 0 sehingga

sinyal outputnya berlogika 1, begitu pula dengan sinyal input bernilai 1 maka

sinyal output bernilai 0 dalam grafik sinyal dimulai dari 1 begitu pula

sebaliknya.

f) Pada Gerbang NOR

Ouput pada gerbang NOR

adalah kebalikan dari sinyal inputnya sesuai dengan prinsip kerja OR yang

dinotkan yaitu aturan penjumlahan jika input 0 maka output nya 1 jika inputnya

1 maka output NOR yang dihasilkan sinyal bernilai 0

g) Pada Gerbang

XNOR

Output XNOR untuk input sinyal CLK bernilai 0 didapatkan input bernilai 1 (

berkebalikan) saat input 1, outputnya sama dengan input sinyal,untuk Gerbang

XNOR prinsip kerja sama dengan XOR yang dinotkan.

2. Bandingkan teori yang ada dengan data hasil praktikum yang didapatkan! Apakah hasilnya sama? Jika iya, jelaskan teori tentang prinsip masing – masing gerbang logika dan jika tidak, jelaskan kenapa berbeda!

Pembahasan:

Dalam percobaan yang telah didapatkan

sama dengan teori tentang masing-masing gerbang logika.

Teori- Teori Gerbang Logika:

1.

NOT = membalikan sinyal input yang ada.

2.

AND = operasi perkalian

dari input

3.

NAND = operasi perkalian

dari input yang outputnya dinotkan

4.

OR = operasi

penjumlahan dari input

5.

NOR = operasi penjumlahan input yang oputnya dinotkan

6.

XOR = Jika input

1 berjumlah ganjil maka output bernilai 1 dan jika input berjumlah genap maka

output bernilai 0

7.

XNOR = output dari gerbang logika XOR yang dinotkan

3. Diketahui bentuk sinyal sebagai berikut.

bagaimana bentuk sinyal yang dihasilkan jika

menggunakan gerbang NOR dan NAND?

Entri yang Diunggulkan

Modul 1 Percobaan 3 Praktikum uP & uC

[KEMBALI KE MENU SEBELUMNYA] DAFTAR ISI 1. Prosedur 2. Hardware dan Diagram Blok 3. Rangkaian Simulasi dan Prinsip Kerja 4. Flow...

.jpg)

.jpeg)