2. Alat dan bahan[Kembali]

A. Alat dan Bahan (Modul De Lorenzo)

1. Jumper

B. Alat dan Bahan (Proteus)

1. IC 74LS112 (JK filp flop)

2. Power DC

3. Rangkaian Simulasi[Kembali]

4. Prinsip Kerja[Kembali]

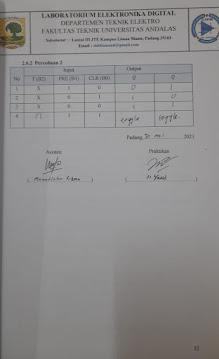

Pada percobaan ini, digunakan IC 74LS112 yang merupakan jenis IC J-K Flip Flop. Dalam percobaan ini, kaki R (reset) dihubungkan ke B0 dengan inputan bernilai 1, kaki S (set) dihubungkan ke B1 dengan inputan bernilai 0, kaki J dan K dihubungkan ke VCC (tegangan referensi), dan kaki clk dihubungkan ke B2 dengan inputan bernilai 1. Output Q dihubungkan ke H7 dan output Q' dihubungkan ke H6.

Apabila dilakukan simulasi, output yang dihasilkan adalah Q bernilai 1 dan Q' bernilai 0. Hal ini disebabkan oleh sifat aktif rendah (active low) pada clk, yang berarti clk akan aktif saat berlogika 0. Karena pada kaki S (set), input yang diberikan adalah 0, maka rangkaian dapat diaktifkan dalam kondisi aktif rendah, sehingga menghasilkan output Q yang bernilai 1. Pada percobaan ini, juga dilakukan variasi beberapa keadaan sebagai berikut :

- Apabila B0=0, B1=1 dan B2=don't care, maka untuk output yang dihasilkan adalah Q=0 dan Q'=1. Ini disebabkan karena clocknya bersifat aktif low, sehingga dia akan aktif ketika diberi inputan berupa 0. Karena pada percobaan ini, tepatnya pada kaki R (reset) diberi logika 0, maka untuk rangkaiannya menjadi bersifat asinkronous reset sehingga outputnya menjadi berlogika 0. Ini sesuai dengan tabel kebenaran yang ada.

- Apabila B0=1, B1=0 dan B2=don't care, maka untuk output yang dihasilkan adalah Q=1 dan Q'=0. Ini disebabkan karena clocknya bersifat aktif low, sehingga dia akan aktif ketika diberi Q'= 0. Karena pada percobaan ini, tepatnya pada kaki S (set) diberi logika 0, maka untuk rangkaiannya menjadi aktif sehingga outputnya menjadi berlogika 1. Ini sesuai dengan tabel kebenaran yang ada.

- Apabila B0=0, B1=0 dan B2=don't care, maka untuk output yang dihasilkan adalah Q=1 dan Q'=1. Ini dinamakan kedaan terlarang, karena kedua ouput sama sama memiliki nilai yang sama yaitu 1. Dimana yang seharusnya untuk nilai Q dengan Q' biasanya nilainya adalah berlawanan. Keadaan ini terjadi saat R (resert) dan S (set) sama sama diberikan inputan 0.

- Apabila B0=1, B1=1 dan B2=toggle, maka untuk output yang dihasilkan adalah Q=0 dan Q'=1. Kondisi ini dinamakan kondisi toggle yatu kondisi disaat outputnya membalikkan nilai output sebeumnya. Dimana sebelumnya output bernilai Q=1 dan sekarang outputnya dibalikkan sehingga nilainya menjadi Q=0. Hasil ouput ini sudah sesuai dengan tabel kebenarannya.

Berdasarkan percobaan yang telah dilakukan, nilai output yang diperoleh sesuai dengan tabel kebenarannya. Hal ini menunjukkan bahwa data yang dihasilkan dapat dikatakan akurat.

5. Video Percobaan[Kembali]

1) Apa yang terjadi jika B1 diganti clock pada kondisi 2!

Jawab:

Jika B1 diganti menjadi clock, maka awalnya B1 terhubung ke S (set) akan berubah-ubah yang masuk ke input setnya karena diganti dengan clock. Konsep dari T flip-flop sendiri mengutamakan R dan S. Saat R dan S (clock) aktive high maka mengikuti output sebelumnya sehingga didapatkan outputnya 0 dan 1. Dan ketika keduanya active low maka nilai yang masuk ke T flip-flop 1 dan 1 di kaki R dan S sehingga outputnya 1 dan 1. Terjadi kondisi toggle atau keluarannya berganti-ganti.

2) Bandingkan hasil percobaan dengan teori!

Jawab:

Dari percobaan yang telah dilakukan, dimana dapat kita lihat contohnya ketika inputnya T(B2) = don't care, B1=1 dan B0=0 maka didapatkan output Q=0 dan Q'=1, saat T(B2) = don't care, B1=0 dan B0=1 maka didapatkan output Q=1 dan Q'=0, dan saat T(B2) = don't care, B1=0 dan B0=0 maka didapatkan output Q=1 dan Q'=1, dan ketika T(B2) dirubah menjadi clock, B1=1 dan B0=1 maka didapatkan nilai Q dan Q' adalah toggle. Hal ini sudah sesuai dengan tabel kebenaran. Dibandingkan dengan teori didapatkan hasil yang sama.

3. Apa Fungsi masing-masing kaki Flip-Flop yang digunakan?

Jawab:

a. Kaki S

Merupakan kaki yang digunakan untuk masukan (input) yang ditandai dengan B1. Kaki S juga disebut kaki set.

b. Kaki R

Merupakan kaki yang digunakan untuk masukan (input) yang ditandai dengan B0. Kaki R juga disebut kaki reset.

c. Kaki J

Merupakan kaki yang digunakan sebagai masukan pengendali, karena menentukan apa yang dilakukan flip flop pada Suatu pinggiran pulsa positif Digunakan dalam pembuatan Tflip flop yang digabung dengan kaki K menjadi satu dan dihubungkan ke VCC.

d. Kaki K

Merupakan kaki yang digunakan sebagai masukan pengendali. Kaki K digabung dengan kaki J menjadi satu dan dihubungkan ke VCC. Ini dihubungkan pada B2.

e. Clock (Kali Clock)

Merupakan kaki yang berperan sebagai Sakelar yang berfungsi mengaktifkan atau mengontrol inputnya.

f. Kaki Q

Merupakan kaki yang menampilkan hasil atau output dan percobaan. Ini dihubungkan pada H7.

g. Kaki Q'

Merupakan kaki yang menampilkan komplemen dari output yang dihasilkan. Ini dihubungkan pada H6.

7. Download[Kembali]

- HTML

- Simulasi Proteus klik disini

- Video Percobaan klik disini

- Datasheet IC 74LS112 klik disini

- Datasheet Switch klik disini