1). Analisalah output yang dihasilkan pada percobaan 1 berdasarkan masing-masing flip-flop!

Jawab:

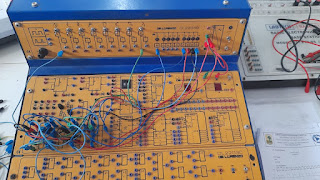

Percobaan 1, 4 buah JK flip-flop saling terhubung dimana ini merupakan rangkaian Asynchronus Binary yang output masing-masing flip-flop yang digunakan akan berguling akibat hanya flip-flop yang paling ujung saja yang dikendalikan oleh sinyal clock (JK Flip Flop yang pertama) sedangkan untuk clock JK Flip Flop yang kedua sampai keempat berasal dari output Q JK flip flop sebelumnya. Setiap JK flip flop membentuk rangkaian T flip flop berlogika 1 sehingga outputnyaa bersifat toggle. Sedangkan untuk clock fall time. Saat clock fall time maka output JK Flip flop awalnya 0 akan mengalami perubahan kenaikan menjadi 1, dan flip flop kedua tidak mengalami perubahan karena dalam kondisi rise time dimana outputnya berlogika 0 begitupun untuk kedua dan ketiga sehingga didapatkan 0001 dengan bilangan desimal 1. Pada timing diagram terjadi delay time pada setiap perubahan output. H0 akan berubah saat fall time clock pertama, H1 berubah saat kelipatan fall time H0 (clk 2) H2 berubah saat fall time clock keempat, dan H3 berubah saat fall time clock ke 8 sehingga terjadi kenaikan pencacah nilai biner 4 bit dari 0000 sampai 1111 lalu kembali ke 0000 dimana didapatkan desimalnya dari 0 sampai 15 dan kembali ke 0 dan seterusnya.

2). Jelaskan kenapa Flip-flop terakhir disebut dengan MSB!

Jawab:

Karena flip-flop terakhir atau H3 memiliki nilai terbesar, dimana saat perubahan dari 0 dan 1 besar. H3 berubah saat fall time clock ke 8 yaitu dari 10000 saat didesimalkan nilainya besar yaitu 8 dan 0000 saat didesimalkan nilainya 0, dibandingkan dengan 0001 dan 0000 itu bedanya cuma 1 dan 0, lebih jauh perubahan yang 1000, karena perubahan yang besar itulah kenapa flip-flop terakhir atau H3 disebut MSB.

- HTML

- Simulasi Proteus klik disini

- Video Percobaan klik disini

- Datasheet IC 74LS112 klik disini

- Datasheet Switch klik disini

.jpg)