- HTML

- Simulasi Proteus klik disini

- Video Percobaan klik disini

- Datasheet IC 74LS112 klik disini

- Datasheet Switch klik disini

Thursday, June 8, 2023

Laporan Akhir 2 Modul 3

Laporan Akhir 1 Modul 3

1). Analisalah output yang dihasilkan pada percobaan 1 berdasarkan masing-masing flip-flop!

Jawab:

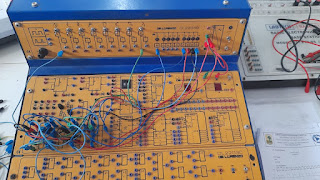

Percobaan 1, 4 buah JK flip-flop saling terhubung dimana ini merupakan rangkaian Asynchronus Binary yang output masing-masing flip-flop yang digunakan akan berguling akibat hanya flip-flop yang paling ujung saja yang dikendalikan oleh sinyal clock (JK Flip Flop yang pertama) sedangkan untuk clock JK Flip Flop yang kedua sampai keempat berasal dari output Q JK flip flop sebelumnya. Setiap JK flip flop membentuk rangkaian T flip flop berlogika 1 sehingga outputnyaa bersifat toggle. Sedangkan untuk clock fall time. Saat clock fall time maka output JK Flip flop awalnya 0 akan mengalami perubahan kenaikan menjadi 1, dan flip flop kedua tidak mengalami perubahan karena dalam kondisi rise time dimana outputnya berlogika 0 begitupun untuk kedua dan ketiga sehingga didapatkan 0001 dengan bilangan desimal 1. Pada timing diagram terjadi delay time pada setiap perubahan output. H0 akan berubah saat fall time clock pertama, H1 berubah saat kelipatan fall time H0 (clk 2) H2 berubah saat fall time clock keempat, dan H3 berubah saat fall time clock ke 8 sehingga terjadi kenaikan pencacah nilai biner 4 bit dari 0000 sampai 1111 lalu kembali ke 0000 dimana didapatkan desimalnya dari 0 sampai 15 dan kembali ke 0 dan seterusnya.

2). Jelaskan kenapa Flip-flop terakhir disebut dengan MSB!

Jawab:

Karena flip-flop terakhir atau H3 memiliki nilai terbesar, dimana saat perubahan dari 0 dan 1 besar. H3 berubah saat fall time clock ke 8 yaitu dari 10000 saat didesimalkan nilainya besar yaitu 8 dan 0000 saat didesimalkan nilainya 0, dibandingkan dengan 0001 dan 0000 itu bedanya cuma 1 dan 0, lebih jauh perubahan yang 1000, karena perubahan yang besar itulah kenapa flip-flop terakhir atau H3 disebut MSB.

- HTML

- Simulasi Proteus klik disini

- Video Percobaan klik disini

- Datasheet IC 74LS112 klik disini

- Datasheet Switch klik disini

Monday, June 5, 2023

Modul 3: Percobaan 3 Kondisi 15

Modul 3

Percobaan 3 Kondisi 15

3. Video [kembali]

Di dalam rangkaian ini terdapat gerbang XOR. Seperti yang diketahui, gerbang XOR merupakan gerbang OR eksklusif, yang berarti outputnya akan menjadi 1 jika jumlah input yang dijumlahkan menghasilkan bilangan ganjil, dan akan menjadi 0 jika jumlah input yang dijumlahkan menghasilkan bilangan genap. Dalam kasus ini, kita dapat melihat bahwa switch S1 dengan logika 0 masuk ke gerbang XOR pertama, dan informasi selanjutnya mengenai jam tidak tersedia.

Modul 3: Percobaan 2 Kondisi 20

Pada rangkaian Asyncronous counter di atas, terdapat komponen input yang terdiri dari 6 saklar SPDT yang dihubungkan dengan vcc (logika 3.3 V) dan ground (logika 0) yang kemudian dihubungkan dengan counter 74LS90 dan 7493.

Pada percobaan , kaki input CKA dan CKB dari counter 74LS90 dan 7493 terhubung ke sinyal clock. kaki input CKA 7493 terhubung ke sinyal clock dan kaki input CKB diumpan balikkan ke output dari kaki QA.

Ouput pada rangkaian di atas mengeluarkan logika 4 bit yang Pada counter 74LS90 dan counter 7448 yang terhubung ke seven segment katoda.

Pada counter 74LS90 memiliki 6 masukan dan 4 keluaran, sedangkan counter 7493 memiliki 2 masukan dan 4 keluaran. Selain itu, Counter 74LS90 akan mengitung atau mencacah desimal 0-9 yakni dari 0000 - 1001, sedangkan counter 7493 akan menghitung atau mencacah hexadesimal dari 0-15(F) yakni dari 0000 - 1111.

Pada counter 74LS90 terdapat 4 kaki masukan yang berguna sebagai reset dan set. Kaki-kaki tersebut adalah R0(1), R0(2), R9(1), R9(2). Kaki-kaki ini bekerja berpasangan, R0(1) dan R0(2) kemudian R9(1) dan R9(2). Jika ketika input kaki R0(1) dan R0(2) di don't care atau diberi logika 0 dan input kaki R9(1) dan R9(2) diberi logika 1, maka counter 74LS90 akan berlogika 1 1 1 1 dan menset

Begitu juga pada counter 7493, terdapat 2 kaki masukan yang berfungsi sebagai reset, yaitu R0(1) dan R0(2). Jika R0(1) dan R0(2) diberi logika 1 dan input kaki R9(1) dan R9(2) di don't care atau diberi logika 0, maka output counter 74LS90 akan berlogika 0 0 0 0 dan mereset, dan pada seven segmen anoda menunjukkan angka 0.

Ketika input kaki R0(1) dan R0(2) salah satunya berlogika 1, dan pada kaki R9(1) dan R9(2) salah satunya berlogika 1,

Demikiian juga pada Pada Counter 7493, ketika input kaki R0(1) dan R0(2) salah satunya berlogika 1, maka akan dalam keadaan counter up asyncronous dan ouput counter 7493 akan menghitung dari 0-15 yakni dari 0000 - 1111 .

Pada IC 7439, kaki CKA digunakan sebagai input A yang berfungsi sebagai pengatur output Q0. Sementara kaki CKB digunakan sebagai input B yang berfungsi sebagai pengatur output Q1, Q2, dan Q3. Pada percobaan kedua ini, rangkaian yang digunakan adalah rangkaian Asynchronous, sehingga kaki CKB menerima input dari output CKA. Oleh karena itu, nilai CKB bergantung pada nilai CKA pada IC 74LS90.

Modul 3 Counter

Counter

Counter

adalah sebuah rangkaian sekuensial yang mengeluarkan urutan

statestate tertentu, yang merupakan aplikasi dari pulsa-pulsa inputnya.

Pulsa input dapat berupa pulsa clock atau pulsa yang dibangkitkan oleh

sumber eksternal dan muncul pada interval waktu tertentu. Counter banyak

digunakan pada peralatan yang berhubungan dengan teknologi digital,

biasanya untuk menghitung jumlah kemunculan sebuah o

kejadian/event atau untuk menghitung pembangkit waktu. Counter yang

mengeluarkan urutan biner dinamakan Biner Counter. Sebuah n-bit binary

counter terdiri dari n buah flip-flop, dapat menghitung dari 0 sampai 2n

- 1 . Counter secara umum diklasifikasikan atas counter asyncron dan

counter syncronous. a. Counter Asyncronous Counter

Asyncronous disebut juga Ripple Through Counter atau Counter Serial

(Serial Counter), karena output masing-masing flip-flop yang digunakan

akan bergulingan (berubah kondisi dan “0” ke “1”) dan sebaliknya secara

berurutan atau langkah demi langkah, hal ini disebabkan karena hanya

flipflop yang paling ujung saja yang dikendalikan oleh sinyal

clock, sedangkan sinyal clock untuk flip-flop lainnya diambilkan dan

masing-masing flip-flop sebelumnya.

Gambar 3.3 Rangkaian Counter Asyncronous b. Counter Syncronous Counter

syncronous disebut sebagai Counter parallel, output flipflop yang

digunakan bergulingan secara serempak. Hal ini disebabkan karena

masing-masing flip- flop tersebut dikendalikan secara serempak oleh

sinyal clock.

Entri yang Diunggulkan

Modul 1 Percobaan 3 Praktikum uP & uC

[KEMBALI KE MENU SEBELUMNYA] DAFTAR ISI 1. Prosedur 2. Hardware dan Diagram Blok 3. Rangkaian Simulasi dan Prinsip Kerja 4. Flow...